To fabricate a prototype of a IC chip is very expensive and it needs from several months up to 1 year to be finished. WHY???

Let’s explore all the designing steps that a CHIP requires…

The fabrication of a prototype IC chip is a highly costly and time-consuming process, requiring significant financial investment and an extended timeline ranging, at least, from several months to even a year for completion.

Imagine, it is like pressing the printing button once the chip is fully designed on the computer

The tape-out of a chip prototype is a very costly and long process. Consequently, it becomes crucial for designers to strive for a successful tape-out without the need for re-design iterations, whenever possible.

In today’s highly competitive market, companies are continuously seeking ways to minimize their time-to-market and launch new products while also reducing costs. On the other hand, research institutes and universities often operate under budget constraints, limiting their ability to engage in multiple tape-outs throughout the year, typically being limited to 1 to 3 tape-outs annually.

Therefore, it becomes imperative for both industry and academia to optimize their design flow, maximize the chances of a successful tape-out, and efficiently utilize their available resources.

A Quick Overview

In the next flow diagram, you have an overview of the full design process for analog integrated circuits with an average estimation of the necessary time for each step for a small project. Although the time needed can vary a lot between different projects and companies, this will give you an approximation.

large and complex projects can extend the design time, especially for the design engineer, up to 6 months or even 1 year, depending on the magnitude. For example, I took part into the design a full inductor-based buck converter, and it needed around a year to be designed.

Short Description of the Design Steps

Some of the previous steps are here described a bit more in detail:

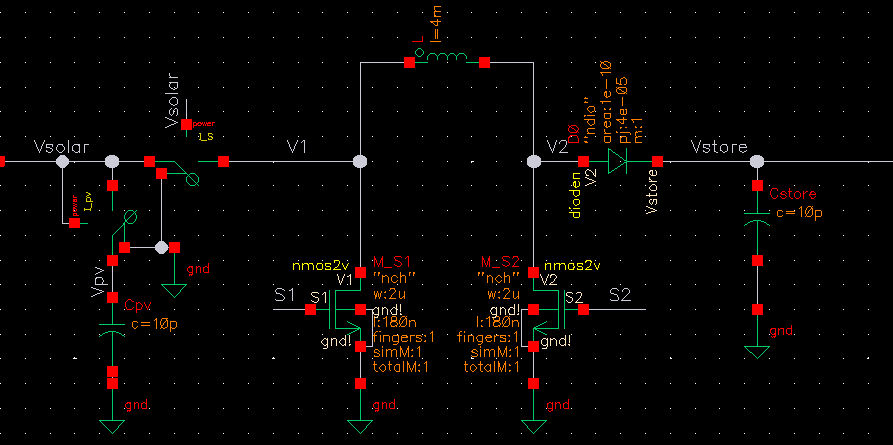

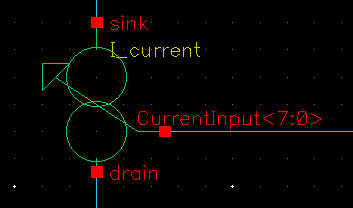

1- Design of the circuit schematic in Cadence Virtuoso. Ensure that all the simulation are correct and the circuit behaves as desired. On the picture below, you can see a small example of how a simple Cadence schematic looks like:

2- Layout generation. When fabricating the circuit, each electronic device has a physical structure in real life. For example, a resistor is a long wire of POLY, a MIM capacitor is two metal layer with an insulator in between. Transistors have a more complex structure with doping regions, metals and poly layers.

All the devices are set together and routed following the schematic connections. Matched transistors or devices need special care and some additional structures have to be added like guard rings or dummies.

3- DRC Check. This test is performed usually with the tool Calibre, which is fully integrated in Cadence Layout Environment. Calibre is a software from Mentor Grpahics and not from Cadence. DRC stands for Design Rules Check.

In this check rules for a proper layout are checked, like space between polygon of the same layers or layers densities. Layers densities (labelled as ‘R’) are ignored here because they are going to be solved later, as it can be seen in the pic below.

4- LvS Check. Here the Layout is compared versus the Schematic. The connections between components are exactly as it is drawn in the schematic. Here is where the possible electric shorts are found.

5- Pass the antenna and Bonding Wire rules. After both checks (DRC and LvS) are passed, these rules ensure that the chip can be manufactured properly without technical problems. For example, long wires in a single metal layer are not desired or vias from the top layer directly to the gate of a transistor neither.

6- Floor Planning. The electric pads are connected to the previously designed block. Also if the chip is composed of various blocks, here they are put together. Also, the number of pins and the pin-out is defined.

7- Dummy filling. The previously chip layout does not fill the 100% of each metal layer. During the fabrication, it is desired that all the layers are more or less equally filled. This is made, excepting critical regions, automatically with a SKILL script. Here is where the DRC rules errors for “densities” are solved.

8- Last DRC and LvS. This check is not strictly necessary, if the previous 3 steps were performed right. But it is a good practice to double-check everything after you may make small changes. An LVS (Layout versus Schematic) with the all the dummies is strongly recommended.

9- Export to a GDS file. The final version is exported in Cadence and sent to the manufacturer.

To do that, go to the CIW window. Then File>> Export >> Stream…

10- Send to the Manufacturer. (“Tape-out”) In our case, we are part of the EuroPractice. This is a program, launched and supported by the EU, aiming to facilitate the access to chip fabrication, reducing the entrance costs, reducing the risks and giving support.

Once the gds file is exported, we send it to our EuroPractice partner which checks the DRC rules and other aspects again. Usually, they find errors or they suggest some changes. After 2 or 3 iterations. The final gds file is ready.

In our case, the partner EuroPractice, sums up many prototypes into a Multi Project Wafer (MPW) and send it to TSMC, which is the real manufacturer.

At the process, we received an email like this:

11- Receive and test the chip. After some months you will receive a low number of dies. The elapsed time ranges from 2 to 10 months depending on many factors. Between 20 and 40 units to test. You can decide if you want to encapsulate it into a package or not. Packaging a prototype die, it is not really cheap, and could cost almost the same as the fabrication.

For an early stage of prototyping, you may want to only measure the fabricated die on-chip with needles. When you have a more developed prototype, you usually want to include it to a PCB, etc. So in this case, it makes more sense to package.

YOU HAVE A SELF DESIGNED ASIC MICROCHIP

In conclusion, this article provided a concise overview of the analog design flow in ICs, with a focus on the often underestimated layout and intermediate steps.

Each of these steps could be explored in much more detail in separate articles, but the intention here was to offer a brief yet informative description with a helpful flow diagram.

This article aims to contribute to spread and broaden the world of analog IC design and inspire further and new designers.

What did you do next with those dies?

How’s the packaging process?

Hello Navadeep

Yes next steps would be to send for packaging… and then it is ready to use.

On developing processes, you maybe test on wafer (without packaging) because price and time.

Best Regards

There are many steps after Die ready. Packaging is next step.

Die placement/ Monolithic or multi die

BGA ball map design

Routing

plane creation for power

SI/PI

DRC

Tapout

From the Design Flow, why do you think fabrication stage is the most critical?

Hello Lee,

Yes, fabrication is quite critical because it is the most uncontrolled step. On the design, you can control or oversee everything but once the chip is fabricated, it is not easy to know what happened during the fabrication, you can only estimate or estipulate…