A digital model and an analogue circuit of a dependent or adjustable current Source is created in Cadence.

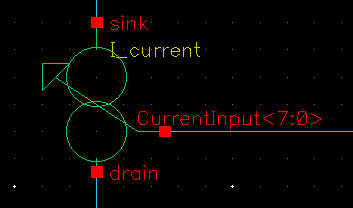

The following dependent current sink varies its current value depending on the 8-bit digital input.

For each increment of the digital input, the current increases one step.

A digital controlled current sink drains a proportional current in function of the digital input signal.

In this example:

- An 8-bit digital vector is used as an input

- The step-size of the current source is set to 1 µA

For example; if the digital input “CurrentInput” is equal to 30, the current source will sink 30 µA.

In the next schematic, it can be seen the idea of the needed blocks: The adjustable current sink itself and a digital counter.

For the variable current sink, first, I will start developing a digital model with vhdl-ams. Then, I will compare it with the analog model.

Adjustable Current Sink

Digital Model

This model is written in VHDL-ams language, but it could be extrapolated to Verilog-a.

For each increment of the input vector, the current increase one step. This step is declared as a generic parameter in VHDL. For this example, the generic parameter is named “rate” and given the value of 0.5 µA.

The full vhdl-ams code of the adjustable current sink:

library ieee;

use ieee.std_logic_1164.all;

use ieee.electrical_systems.all;

use ieee.numeric_std.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity Csink is

generic(

rate : real := 1.0e-6 --current step size

);

port (

signal CurrentInput : std_logic_vector(7 downto 0);

terminal sink,drain : electrical

);

end Csink;

architecture vhdlams of Csink is

quantity IR through sink to drain; --IR is the current between both ports

signal converted : integer; --For convert the input std_vector

begin

converted <= CONV_INTEGER((CurrentInput)); --Convert the std_logic_vector to integer

IR == real(converted)*rate;

end vhdlams;

For test this module the control signal (std_logic_vector) is provided from the counter block.

The simulation wave diagrams show the behaviour:

Analog circuit

A simply analogue circuit was created with the help of an ideal current source (set to 1 µA). The circuit is just a current mirror with 255 branches.

The output branch has 255 transistors to enable each branch. Therefore, it can be chosen exactly how much current is sunk on the drain pin.

Important Note: to instantiate 255 transistors, it not necessary to “draw” them one by one. You can simply rename the transistor with the suffix “<0:255>“. It will automatically make it for you!

The schematic diagram:

Thermometer Coder

The thermometer or unary code is needed in the variable current sink to drive the 256 branches of 1 uA. As you can see in the previous schematic, we need the so called “Thermometer Coder” block.

What is a thermometer coder?

[cuatro texto=’The thermometer code converts a n-bit vector into a series of ones followed by zeroes of size 2^n’]

In this case, we want to transform an 8-bit input vector into a 256 output vector.

The thermometer coder block is written in VHDL with the following code:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity thermo is

port

(

vector_in : in std_logic_vector(7 downto 0);

vector_out : out std_logic_vector(255 downto 0)

);

end entity;

architecture vhdlams of thermo is

signal salida : std_logic_vector(255 downto 0) := (others => '0');

begin

process(vector_in)

variable intermediate: integer range 0 to 255;

begin

intermediate := CONV_INTEGER((vector_in));

salida <= (others => '0');

for i in 0 to intermediate loop

salida(i) <= '1';

end loop;

vector_out <= salida;

end process;

end vhdlams;The functionality of the thermometer coder can be seen below. Note that as we have 256 signals, they can not fit on the screen, and it is not so visually.

Test Bench

The test bench to prove the functionality of this digitally dependent current sink is shown below. The digital counter, explained in the other article, is now reused as stimuli to create a digital ramp as depicted in the diagram below.

The test signal is an 8-bit ramp (with 256 steps) that is coming to the 256 transistors

Digital vs analogue model

Theoretically, the digital and analogue versions should behave identically, isn’t it?

Yes!!! the analogue circuit performs similar, but slightly different because of non-linearities.

The digital model behaves as programmed, each step of the input is translated into current linearly, as shown in the following Figure.

Zoom of the digital model and analogue circuit compared: