What is the Body Effect in CMOS Transistors and How influences the Threshold Voltage Vth

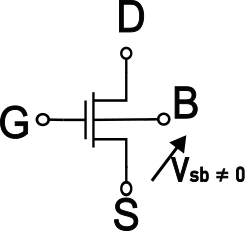

The Body Effect is one of the 3 most important second-order effect of the MOSFET devices, together with channel-lenght modulation and subthreshold conduction. …

What is the Body Effect in CMOS Transistors and How influences the Threshold Voltage VthRead More »