Charge Injection is caused by the switching action of the MOSFET, resulting in a brief injection of charge into the signal path, leading to voltage glitches.

The charge injection effect in CMOS analog switches negatively influences their performance, resulting in voltage spikes due to the release of stored charge in the gate-to-drain parasitic capacitance. This is critical for many applications such as any kind of sample-and-hold circuit, ADCs, precision amplifiers or high frequency RF circuits among others.

This short article explores the mechanisms behind charge injection, its impact on circuit behavior, and an overview of various techniques to mitigate its effects. Understanding these concepts is essential for designing high-performance analog circuits with minimal signal distortion.

What is Charge Injection in CMOS Circuits?

The gate-to-drain parasitic capacitance of the switch transistors store a small amount of charge when they are conducting and releases it once they are disconnected.

The effect of charge injection is a voltage glitch on the output when switching, caused by the “injection” of the stored charge from the stray gate capacitance.

The charge Q at the turning off moment can be calculated multiplying the area of the device, the overdrive and the oxide capacitance per unit area:

Q = Cox·W·L· (Vgs – Vth)

The amplitude of the glitch depends on the rise and fall times of the signal and the load capacitance at the output. Since the amount of charge is fixed, larger output capacitance reduces the charge injection effect. Conversely, longer turn-on and turn-off times result in the same fixed amount of charge being injected over a longer time period, reducing the glitch amplitude.

Trade off: Charge injection vs On-resistance

The resistance of a transistor decreases with increasing size. Larger Nmos and Pmos devices have larger stray gate-capacitance, leading to more charge accumulation per cycle. Lower on-resitance leads to more charge injection.

Charge Cancellation Techniques in Analog Switches

Some charge injection cancellation techniques are employed to mitigate the effect and improve the performance of analog switches.

Well-designed Layout Matching

A nice layout helps to minimize the parasitic capacitances and ensures symmetry.

However, stray gate-to-drain capacitances are never perfectly matched, which lead to unequal amounts of positive and negative charge are injected onto the drain path.

Complementary Switch Configuration

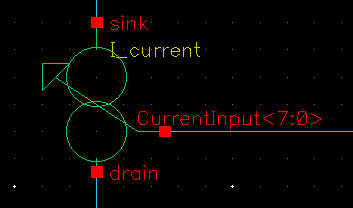

Using complementary CMOS switches with a Nmos and Pmos devices in parallel partially cancel the charge injection.

The charge injected by one transistor can be partially canceled by the opposite charge injection from the complementary transistor. The NMOS and PMOS inject opposite polarity charges due to their opposite channel types (carriers and holes), helping to reduce the overall charge injection.

However, perfect charge injection compensation is limited by potentially slightly differences in the overlap stray capacitances.

Additional Dummy Switches

Adding extra dummy switches before and after the analog switch help to reduce the overall charge injection and minimize the clock feedthrough (continuous coupling of the clock signal through parasitic capacitances).

Balanced /Unbalanced Switches

Pmos devices are often sized to be 2.5x times larger than the Nmos counterparts to ensure both devices have the same on-resistance and similar dynamic behavior. This compensates for the fact that the electron carriers mobility (nmos) is more than 2 to 4 times greater than the holes (pmos). As a result, Pmos devices have a higher gate stray capacitance and therefore can store more charge.

Differential Signaling Circuits

In fully differential circuits, two complementary switches are used for the positive and negative signal paths. Charge injection effects on each signal path tend to cancel each other out due to their opposite polarities.

As a result, the net charge injection effect on the output is significantly reduced or even eliminated.

Charge injection in Single Transistor Switches

Charge injection effects are more significant when using a single transistor as an analog switch.

In such cases, implementing techniques to cancel charge injection becomes more relevant. One of the most straightforward methods is adding dummy transistors.

A dummy transistor is added in the circuit to counteract the charge injection, as shown in the schematic below. This dummy transistor is designed to inject an equal but opposite charge to the signal path, effectively canceling out the charge injection from the main switch.

The width of the dummy device must be the half of the switch transistor, as we assume that half of the charge is injected into the drain and the other into the source.

The dummy transistor must be of the same type and must be controlled by the counterpart signal, as shown in the schematic below. We can instantiate 2 dummy devices (one at the source and another at the drain) or just 1 at the drain. It depends if the charge injection on the source is critical or not. Its sole purpose is to provide or absorb the gate capacitance charge to avoid that this is injected to the signal path.

In conclusion, charge injection in CMOS analog switches could be a critical issue in sensitive applications such as sample-and-hold circuits, ADCs, precision amplifiers, and high-frequency RF circuits, manifesting as voltage glitches that severely impact performance.

Understanding the mechanisms of charge injection and implementing effective cancellation techniques are essential for designing high-performance analog circuits. Techniques such as well-designed matching, complementary switch configurations, dummy transistors, and differential signaling circuits play important roles in mitigating the effects of charge injection.

By employing these strategies, designers can significantly reduce signal distortion and enhance the overall performance and reliability of analog switches in CMOS integrated circuits.

It will be helpful to everyone who utilizes it, including me. Keep up the good work – looking forward to more posts.