Generating complementary clock signals from a single oscillator signal is straightforward with the so-called non-overlapping block.

Let’s analyze it!!

Often, 2 complementary clock signals are needed, where only one clock edge is active at a time. Meaning that the rising and falling edges of the clock are separated in time.

In the following diagram, it can be seen clearer…

Why do we need a non-overlapping clock?

Without going into much detail:

In sequential circuits, we need to avoid the so-called “Race Conditions”.

In complementary switches (Nmos + Pmos), if the two clock signals overlap, it creates a direct path between the power supply and ground through the conducting nmos and pmos transistors. Even for a very short period of time, this should be avoided.

In all cases, the overlap reduces drastically the efficiency, and in some other cases it can generate a very high current that burns or heats up the device.

The Dead Time is the period when both clock signals are zero or low.

Circuit Schematic

The basic schematic can be found in the next figure. This implementation is the simplest circuit and it is based on inverters to generate the delay between both signals.

To increase the dead time, you may add more inverters in the row or add some capacitor element in between.

The following implementation of the non overlapping module adds a capacitor in both delay lines. Adjusting the size of the capacitor, we can manage bigger delays and therefore, dead times.

How to control or regulate the Dead Time?

The dead time of a non overlapping clock must be optimized according with the trade off:

- Long enough to avoid at any case Shoot-Through current under any condition

- Short enough to don’t lose too much efficiency

We have to leave some margin to avoid the shoot-through at any corner, temperature, process variation, operating voltages, etc. For that we need a reasonable margin in time.

However, the trade-off is that if we leave too much time during the dead time, the system (charge pump, etc) is not operating, so the power loss and a decrease of the overall efficiency.

The dead time regulation can be done with various methods and techniques, the most common and simple are based on:

- Inverters

- Capacitors

- Clock cycles

In the other article, I talked more in detail about the most common delay elements in CMOS circuits and how to implement them.

For non-overlapping clock modules, a set of inverters in series mixed with some capacitor devices is commonly used.

The inverter based circuits are simple and require a small silicon area, but each inverter only adds a few nanoseconds of delay, depending on the technology and other conditions. Although, the delay of an inverter (known as switching time or propagation delay) can be modified through techniques such as current starving. If we want to generate a considerable delay only with inverters, we would need a lot of inverters. In these cases, a capacitor device is more convenient in terms of silicon area optimization.

Delays based on clock cycles are not so common because we need to have available a fast clock signal in the circuit, which is at least 16 to 100 times faster than the main oscillator. To implement this technique, we add a flipflop to create a delay with a duration of one or more clock cycles. Then, we use this delay to implement the dead time for the non-ovelapping clock module.

Example: Cadence Simulations of a Non-Overlapping Block

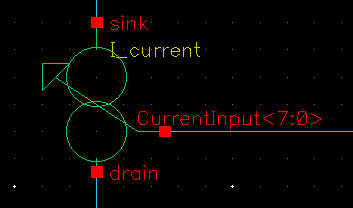

To perform a simulation and to have a clean testbench, I created a symbol with the non-overlap circuit inside. For simplicity, I didn’t implement the enable EN, so I left it unconnected.

In this example, the input clock signal is generated by a pulse voltage source and the outputs are the 2 non-overlapping clock signals A and B.

A transient simulation is performed to observe the clock behavior. We can see that the dead time of the non-overlap module. The dead time is the time slot where both complementary signals are grounded.

The dead time using a 1.33pF capacitor and 2 inverters is only 2.77ns, which is usually too short to rely on a real circuit in silicon.

To widen the dead time, we must increase the delay element. The “easy” and fast solution is to increase the number of inverter in the chain or to add more capacitance in between. However, we can’t add inverters infinitely, because of power consumption and silicon area utilization constraints. The other straightforward solution is to increment the capacitance in the inverter chain, to slow down the propagation delay of the inverters.

In this second attempt, I am using a 10pF capacitance, so we can see after the simulation that the dead time is increased from 2.8ns to 17.7ns, but at cost of silicon area.

Let’s check the intermediate nets: