This auxiliary block in Cadence is a Nice to Have in your Library!

This block stops or finishes a Cadence transient simulation when an output signal reaches a desired value.

Managing simulation time effectively is crucial, especially for long transient simulations, such as corners or parametric analyses.

Optimizing the running time can be a game-changer

This VerilogA block/code enables you to stop automatically the current transient simulation in Cadence Virtuoso depending on any analog condition, in this case, a target signal value.

Optimize your Simulation with this Handy Auxiliary Block

This “simulation stop” block is perfect when you need to perform multiple and long simulations to save valuable computational resources.

What does This Block Do?

- Stops the current transient simulation in Cadence Virtuoso based on analog conditions.

- Perfect for long and repetitive simulations, saving significant time by terminating runs when predefined criteria are achieved.

VerilogA Code Example

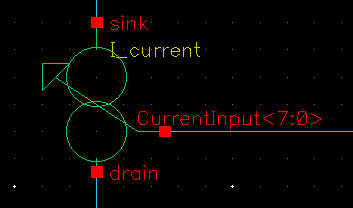

This block monitors a specific signal and stops the simulation when the desired signal reaches a target value.

///////////////////////////////////////////////////////////////////////////

// Engineer: Alberto Lopez

//

// Description: stop the simulation when the input voltage arrives to a minimum value

//

// Change history: feb/2021

//

/////////////////////////////////////////////////////////////////////////////

`include "constants.vams"

`include "disciplines.vams"

module FINISH_run( vin, GND );

inout GND;

input vin;

electrical GND;

electrical vin;

//Parameters

parameter real tiempo = 1u; //refreshing time for the Verilog code

parameter real MIN_VOLTAGE = 2; //Min voltage level to trigger the

integer flag;

analog begin

@(initial_step) begin

flag = 0;

end

@(timer(0,tiempo)) begin

if( V(vin,GND) > MIN_VOLTAGE ) begin

flag = 1; //only for testing purposes

$finish(0); //command to stop the current simulation

end

end

end //analog

endmodule

How does it work

The functionality of this block is quite simple.

I created a simple testbench with the previous stop cellview and a voltage source with a ramp signal at the input signal.

First, I will check only the input ramp signal by commenting out the VerilogA code. Note: to comment out or ignore a block in Cadence, you must press the keybinds CTRL+del. Other Cadende Keybind can be found on this list.

The input signal with 4ms of transient simulation time looks like:

Full test bench simulation: Activating the Verilog stop block and re-running the transient simulation, we can see that, although the simulation time was set to 4ms, the simulation was stopped by the external block at 360us. The verilog variable stop_flag was raised at 335us (yellow) and finished the simulation.

Reading the log window, we can verify that the simulation has been stopped by an external trigger.

Stop after a predefined delay

This block variation is similar to the previous one, but includes an added delay. The Verilog block will stop the simulation when the flag is raised after a specified amount of time.

You can modify the time delay with the parameter DELAY_TIME, which is initially equals to 1000 microseconds.

Code:

///////////////////////////////////////////////////////////////////////////

// Engineer: Alberto Lopez

//

// Description: stop the simulation when the input voltage arrives to a minimum value

//

// Change history: feb/2021

//

/////////////////////////////////////////////////////////////////////////////

`include "constants.vams"

`include "disciplines.vams"

module FINISH_run_delay( vin, GND );

inout GND;

input vin;

electrical GND;

electrical vin;

//Parameters

parameter real tiempo = 1u; //refreshing time for the Verilog code

parameter real MIN_VOLTAGE = 2; //Min voltage level to trigger the FINISH

parameter real DELAY_TIME = 1000; // number of "tiempo" steps to execute the stop action

integer flag;

integer cnt;

analog begin

@(initial_step) begin

flag = 0;

cnt = 0;

end

@(timer(0,tiempo)) begin

if( V(vin,GND) > MIN_VOLTAGE ) begin

flag = 1; //only for testing purposes

end

if (flag == 1) begin

cnt = cnt +1;

if (cnt == DELAY_TIME) begin

$finish(0); //command to stop the current simulation

end

end

end

end //analog

endmodule

How to generate sine look up table in verilog code

Hello,

Your can check my other post, where I talk about sinus wave generation with look-ups tables

Best Regards

I tried to use $finish(0) in an MC sim, but that ends the simulation after the first run (nom run). it doesn’t end the current run only. is there any other command to do so?

I’ve got a similar problem. When using VerilogA module with $finish in MC, every run ends up with “sim error”.

In the simulator log I found this:

(…) To stop the current transient analysis without stopping the simulation, use the ‘$finish_current_analysis’ function instead of ‘$stop’.

I’ve replaced $finish with $finish_current_analysis and now it works also for MC 🙂

Thanks for the valuable info 🙂

Hi ALberto,

I am trying to implent a “delay” function in verilogA model, e.g. an oscillator, because the oscillator should not run before others power up. Could you please give me some advice?Thanks!

Hello Wellgod,

I would implement a trigger with the POR signal you may have instead a delay-based model.

Best Regards

Alberto