Several methods can be used to measure with Cadence Virtuoso the offset voltage of an operational amplifier (op-amp) using only simulations.

The offset voltage in op-amps is an inherent characteristic of the circuit, resulting from mismatches in transistor characteristics, overdrive voltages, and layout imperfections.

Contents

The Offset in Op. Amps

The offset error is unavoidable. Simply it is inevitable that an operational amplifier is unbalanced, generating a DC offset error. The most common errors in operational amplifiers are offset errors together with temperature drift and Fllicker (1/f) noise.

Why exists the Offset?

Offset voltage arises due to inherent mismatches and imperfections in the internal components of the op-amp, particularly the transistors that make up the input differential pair.

- Threshold Voltage (Vth) Mismatch: The two input transistors should ideally be identical. However, due to process variations during fabrication, the threshold voltages of the transistors may differ slightly. This difference causes the transistors to require slightly different gate-source voltages to conduct the same current, leading to a small voltage difference at the input terminals, which produces a voltage offset.

- Transistor Geometry Variations: Any mismatch in the W and L dimensions between the transistors in the differential pair leads to unequal current distribution, resulting in an offset voltage.

- Process Gradients: Across the silicon wafer, there can be slight variations in doping concentration, oxide thickness, and other parameters. These process gradients contribute to the offset.

- Parasitic Effects: Differences in parasitic capacitances and resistances in the layout, caused by variations in routing, lead to mismatches and offset.

- Mismatches Due to Temperature: If the two transistors in the differential pair experience different local temperatures or have different temperature coefficients, their characteristics will diverge as the temperature changes, leading to an offset voltage.

- 1/f (Flicker) Noise: This low-frequency noise can contribute to the offset voltage, especially in low-frequency applications.

The most effective rules to reduce the offset in differential pairs are:

- Use Larger geometries. Larger devices damp the imperfection of the edges of the fingers. Although, the bigger the devices are, the slower switch the transistors due to the gate capacitance.

- Common centroid: A well-executed layout with a common centroid, compensate the inevitable process gradients in two axis of the wafer. But, it is not 100% effective.

- Moreover, techniques like trimming, auto-zeroing, and chopping can reduce or compensate the offset voltage up to 1 uV level. They are employed in precision applications to further reduce the impact of offset voltage.

Measure the Offset of an Op- Amp.

The most straightforward and simplest methods to measure the offset of an Op. Amp with a simulation are studied in this article with a practical example.

The Op. Amp. Circuit

For this example, I chose a basic 2-stage operational amplifier including some enabling switches. The op-amp. is partially asymmetric, which infers an offset-prone design (valid for this case).

Notice that If we use a totally symmetric design with ideal components… no offset will appear!!

Offset Calculation Methods

1- Manually setting the offset

The op- amp is connected in open-loop configuration. The inputs are tied to a common bias level, which is typically half of the supply voltage (Vsupply/2). This ensures that the inputs are balanced and any output deviation is due to the inherent offset of the op-amp.

At one input, the minus one in this example, is connected to a DC source, which is swept until the output voltage is centered to the vsupply/2.

The DC vdc source used in this example to compensate the offset is V20. The increments must be small to accurately calculate the offset.

The test bench is depicted in the schematic below. The voltage source V20 has a parametrized dc voltage with the parameter “voffset”.

The common mode voltage, in this case, labeled as vref, which is chosen vsupply/2 (1.8V/2=900mV).

The value of “voffset” is parametrized with a starting estimated range, in this case from -2mV to 2mV. The range is later iterated depending on the simulation results.

For the simulation, we can use a DC simulation or a long enough transient simulation (to avoid the influence of the own op.amp. delay).

DC simulations are preferred versus transient simulations, because they are much faster and precise, but in dc simulations, we have to make sure that the op-amp. is biased properly.

In the plot of the results of the DC simulation, we plot the Vout voltage vs the “offset” parameter to check where the output is equal to vdd/2. In the example below, the offset voltage is estimated to be 585uV.

For double check and confirm the results, I like to perform a transient simulation will confirm the obtained value.

I set the previous obtained offset value to the dc vdc source, 585uV, and perform a long transient simulation. The output voltage must be balanced to vsupply/2.

2- Output Calculation with the Gain

This method to measure the offset in an op- amp. is only valid when we know the value of the dc gain. I explained it in other article How to Measure the Gain of an op-amp with simulations.

The setup is done connecting both inputs are to Vsupply/2 or another bias level. The output voltage is measured.

The offset at the output is the deviation, the difference between the output voltage (Vo) and the bias voltage (Vsupply/2).

The input-referred offset voltage can be calculated dividing the previous deviation by the DC gain:

The input-referred offset voltage (Vos) represents the small voltage difference between the inputs of the op-amp that is causing the output to deviate from its ideal balanced value.

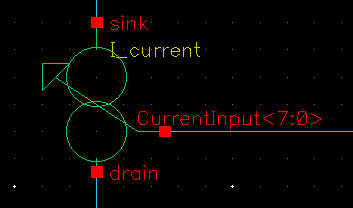

3- Unity Gain Buffer Connection

Configuring the op-amp. under test in unity gain buffer mode, as depicted below. The output is feedback to the inverting input (minus), and the positive input (+) connected to the input voltage.

In this configuration, any voltage difference between the inputs, which is the offset voltage, will be seen directly at the output.

In a perfect op-amp with no offset, the output would exactly match the input voltage.

![]()

This method will give you the possibility to include the offset value as an output metric, which will be very useful to make corners, MC, etc.

The test bench can be seen on the following schematic:

To add an output “offset” equals to the output voltage minus the reference voltage.

The results of simulating the previous test bench, with a simply PVT corners are:

In this article, we have explored various methods to measure the offset voltage of an op-amp using Cadence simulations.

As the Offset Voltage is an inherent characteristic of op-amps and unavoidable…

…understanding this offset is crucial for designing robust analog circuits!!

Hi Alberto,

This is Bellamkonda, I am very thankful to you for sharing the valuable and important content for IC Design beginners and also whoever not aware of it. I request you to continue your efforts and keep going. Your effort is