A typical problem in integrated circuits is distributing a digital signal to a very large node, such as clocking for registers, memories and counters. The propagation delays and skew must be minimized to avoid malfunctions.

While the tapering ratio is recognized as a significant metric in the sizing of digital logic gates, it tends to be an underappreciated concept in analog design.

The common approach to distributing a signal across a large number of nodes is to use a chain of cascaded buffers (also referred as “tapered inverters”), which gradually amplifies the signal.

Each stage drives the next stage with an increasing capacitive load, but maintaining the same ratio to ensure an optimal signal propagation.

The goal is to minimize the overall delay through the inverter chain.

Fanout of Cascoded of Buffers

To minimize propagation delay, the load is increased gradually across the multiple stages, ensuring that each stage has the same fanout. A uniform fanout across the chain optimizes the time delay.

The total load that the final buffer must drive is the cumulative capacitance of all the nodes at the end of the chain.

The fanout can be defined as the ratio of the output and input capacitors

Fanout is the ratio of the output capacitance to the input capacitance of a buffer or logic gate. It quantifies how much load (capacitance) a buffer is driving in relation to the input capacitance of the buffer.

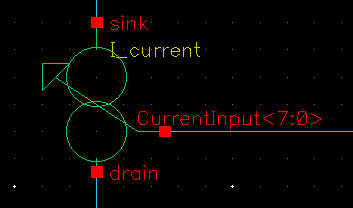

For example, in a Common Source stage with an ideal current source:

There are 2 different optimizations:

- How should the inverters be sized to minimize delay?

- How many stages are needed to minimize the delay?

The total delay is minimized for an optimum fanout per stage because larger fanout values lead to slower individual stages (due to increased capacitance on each stage), while smaller fanout values lead to unnecessarily large numbers of stages, which also increases the total delay.

Why not set a single very large inverter to reduce the time delay?

The input gate capacitance of the inverter would be so large that the digital signal may not be able to drive that load. Therefore, we would still need a gate to drive this inverter.

Optimum Fanout of Inverters

Thus, there is an optimum fanout that minimizes the global propagation delay.

The Optimum Fanout for a chain of N inverters

- All inverters have the same fan-out

- Fanout per stage = (C_Load/Cin)^(1/N)

The mathematical expression for the optimal fanout is:

Starting from the previous optimum fanout f, now, we calculate the N.

Introducing the intrinsic delay factor or self-factor γ (gamma), represents the intrinsic parasitics of the gate. All the gates have an intrinsic delay, which is the time it takes to switch without any external load. In practical CMOS technologies, the value of γ ranges between 0.5 and 1.

We can now express the total delay as a function of Cin, Cout, f (optimum) and the self-factor γ, where Tinv is the time delay of each inverter.

The total delay can be plotted versus the fanout depending on the self-loading factor γ

For the ideal case ignoring the self-loading (γ=0), N = ln(C_L/Cin), so the effective fanout becomes f = e = 2.72

Considering the self-factor (γ>0),

In practice, for CMOS circuits, the optimum fanout is typically around 3 to 4. This is derived from mathematical modeling and empirical testing, which show that when each buffer in the chain has a fanout between 3 and 4, the total delay across the entire chain is minimized.

A popularly used rule of thumb in digital electronics, known as “Fanout of 4” rule (FO4), specifies an optimal fanout of 4, helping designers to balance performance, power and area.

Final Conclusions

- To optimize the time delay in cascaded buffer chains in integrated circuits, the optimum fanout per stage is crucial.

- The fanout, defined as the ratio of output to input capacitance, should be uniform across all stages to minimize propagation delay.

- A single large inverter is inefficient due to its large input capacitance, making a chain of smaller inverters more effective.

- The optimal fanout typically falls between 3 and 4, balancing performance, power, and area. This is supported by the “Fanout of 4” (FO4) rule, widely used in digital electronics.