Why are the LDOs mainly built with pmos as a pass transistor and not with nmos devices?

LDO circuits are a type of voltage regulator, commonly used in integrated circuits. LDO stands for “Low Dropout”.

The main function of an LDO is to provide a regulated and stable voltage, maintaining a stable voltage level despite variations and noise in the input voltage (supply), temperature and process. The LDO supplies other blocks, such as ADC, sensors, analog signal processing, clocks, vrefs, etc, which require a stable power supply for proper functionality.

The LDOs include a feedback mechanism to continuously monitor the output voltage, working in closed-loop. This feedback is used to adjust the internal circuitry and maintain a constant output voltage despite variations in the input voltage or load conditions.

LDOs Topologies

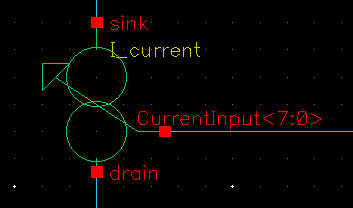

The standard topology can be seen in the following diagram:

First, Let’s analyze all the elements:

- A voltage reference signal coming from a bandgap is used as a stable reference for the regulator.

- An error amplifier (EA) detects differences between the feedback value and the voltage reference and adjusts the pass-element resistance. Usually it is implemented as an OTA.

- Feedback resistor network divides the output voltage to compare it with the vref voltage.

- The pass-device, pass-transistor or pass-element (usually a MOSFET) adjusts its resistance between the input voltage to the regulated output voltage to keep it inside the specified range.

In the industry real applications, the pass device is implemented as a pmos transistor. Let’s see the differences if we use a pmos or an nmos.

Nmos vs Pmos LDO Architecture

PMOS LDOs dominate the industry because of the low dropoff voltage, but the use of NMOS as a pass transistor makes sense when the power supply voltage is much greater than the regulated output voltage.

The nmos configuration acts as a common drain (or Source follower) with positive gain, and the pmos acts as a common source element with negative feedback. Therefore, the polarity of the op amp must be adapted to the case.

Both can be used, but PMOS LDOs are much more frequent.

Why is the Pmos widely used?

Mainly because the dropout voltage is much smaller. Let’s analyze the case:

PMOS

The output of the error amplifier (EA_out) in pmos can move between GND and Vin-Vth region (see in the diagram below) and the dropout voltage is only depending on the Vds (which can be around 50mV for saturated devices).

NMOS

In the nmos architecture, the minimum voltage output of the error amplifier to turn on the pass-transistor must be at least a Vth more than the output voltage.

So, the output regulated voltage is limited to a threshold voltage less than the input voltage + a margin for loop regulation. Also, we can say that the minimum dropout voltage is, at least, a Vth. Moreover, the pass-device is typically a high-power and/or high-voltage transistor because it must drive a relatively high current/voltage. The threshold voltage (Vth) in such devices is often higher than the standard 1V transistor.

Summarizing: PMOS topology required less input voltage (Vout + Vds = Vout + 100-200mV) while NMOS required Vout +vgs = Vout +500-800mV

NMOS Architecture Advantages

In some cases, the nmos topology can be positive and have some relevant advantages:

Size: As the mobility of the electrons in nmos is 3 to 5 times higher than the pmos holes transistors (𝝁_n > 𝝁_p). This implies that the size of the pass-device would be 3 to 5 times smaller transistors to achieve the equivalent driving strength.

Frequency compensation: In nmos, the dominant pole often is at the gate of the nmos pass transistor instead of at the output node. This translates into better stability.

The output impedance is lower. The output resistance can be calculated from the parallel resistance of the feedback and the ro, as the following formula:

Regarding the ro, in the nmos pass transistor case, it is connected as a common drain (source follower) and therefore it leads to a smaller output impedance (ro).

In general, a low output impedance for a voltage source is desired (and infinite impedance for current sources).

The Power Supply Rejection Ratio PSRR is also better.

NMOS cons

Higher dropoff voltage. I.e. we need more input voltage to generate the same output.

The drop off voltage in pmos is smaller, you can even achieve 50 – 100mV easily.

Possible Alternatives for NMOS LDO devices

Nmos pass devices can be used if we overcome the main drawbacks. For that, some of the common tricks are:

Use a native nmos transistor, so the vth is minimized. Although the nmos device can’t be switched off totally, we would need to add other mechanisms to turn off the LDO.

Supply the error amplifier (Vdd-EA) with a higher voltage than the input voltage (Vin) to minimize the dropoff voltage. Sometimes, this can be done with a charge pump if any higher voltage than Vin is available.