Analog circuits schematics are designed and simulated with ‘realistic’ models in Cadence, estimating roughly how the circuit will work in the real world.

When a circuit is taped out and fabricated on silicon with any VLSI technologies, the behaviour could vary from the simulated one.

Contents

Why is back annotating important in Circuit Design?

The major purpose of parasitic extraction is to create a more accurate and realistic analog model of the final circuit.

Real circuits are far from behaving as the simulations in Cadence

This allows run more realistic simulations at the end of the analog design flow by updating the circuit model into a more realistic one, based on the physical layout. In this way, it is ensured proper functionality of the design and a better representation of the final silicon die behaviour.

Think that everything you draw in the layout, involves the creation of parasitic.

Parasitics are everywhere…

- Every single route on the metal or via layer is, in fact, a resistor, a small resistor on the best cases, but at the end of the day a resistor.

- Every two conductors or conducting surfaces split by an insulator implies the creation of a stray capacitor.

Depending on the circuit, this can have a huge influence on the final behaviour of the design.

Parasitics may cause distortions like:

- Impulse Response drop

- Crosstalk

- More capacitive loading

- Inductive coupling

- Increased delays

Reviewing the backend design flow:

Layout generation >> DRC >> LVS >> Parasitic extraction >> Post Layout Simulation >> Final Layout >> Tapeout

The back annotation is performed after the parasitic extraction. You should get a file named “<filename>_extracted” in Cadence.

[file back annotated en Cadence]

After Parasitic extraction, ideally, it would be nice to perform a full chip post-layout sim, but this is not always possible due to the high required computing power.

- The digital parasitics are transformed into delays by the “Timing Calculator”. These digital delays are standardized on “Standard Delay Format” (SDF) -file. Also, if you program any FPGA, you get this SDF file, for example in Vivado.

- On the analogue blocks, parasitic capacitances and resistances are added to the analog model. A post-layout simulation with the extracted view is very convenient to take “all the circuit” into account.

l then be able to re-simulate your design with extracted parasitics

Parasitics extraction options

There are many possibilities and parameters to configure when extracting:

- Method: xRC or xACT_3D. Normally 3D extraction required a lot of computational power, so the classical xRC set-up is chosen.

- Type: R only, R+C, C only, R+C+CC, etc. For the RC types, it would depend on how big your circuit is or how much does the parasitics affect to your circuit. You can set it to R+C as standard configuration.

- Inductance: No, self and mutual inductance. The stray inductances are not so relevant in baseband frequencies (not RF designs at low frequency)

- Nets: only selected nets, exclude some nets or all the circuit. If there is any critical routes on the circuit, you may analyze them in detail.

In the following pics, you see graphically the meaning of RC or RC+CC:

Extracting the Parasitics in Cadence

After the layout is finished (and it passed the DRC and LVS checks), you can extract the parasitic in the layout window, Calibre >> Run PEX

From the previous parasitics extraction options, the standard (conservative) config is xRC, Transistor Level, RC and No Inductances.

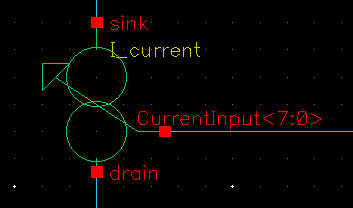

Parasitics Visualization

You can back-annotate your schematics and layouts with the extracted parasitic capacitors, resistors, inductances…

Once the extraction finishes, you can always visualize the stray components in context overlaid on the schematic or layout. Go to Calibre>> Setup >> Calibre View. On the Calibre View Setup Window, you can modify the configuration parameters to overlay the parasitics on your schematic or layout view.

Spoiler The back annotate views are not so… visually “nice” or helpful. There are too many components, they are unordered, overlapped, etc

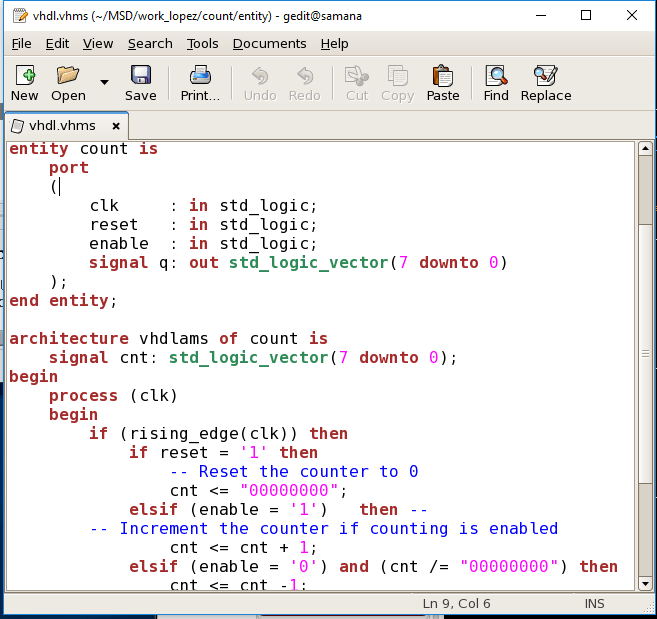

Re-simulating the extracted layout in Cadence

For this, you need to create a config file (if you don’t have it already) associated to your schematic view. The same procedure, as you were simulating mixed-signal circuits, where you have to choose between model, digital or schematic views.

Later, in the assembler (or ADE) view, you must select the ‘config” view as default. For that, right-click on the “Test” and then choose ‘config’ on the view name.

On the config file, you must configure, which view should be used. In my case, I chose “calibre_xRC_RC” for the charge pump.

Now, you can run the simulation, as usually, in assembler (or ADE) and it will use the post-layout extracted view.